#### ARTICLE IN PRESS

Materials Science in Semiconductor Processing ■ (■■■) ■■■=■■

FI SEVIER

Contents lists available at ScienceDirect

### Materials Science in Semiconductor Processing

journal homepage: www.elsevier.com/locate/mssp

# Very low leakage InGaAs/InAlAs pHEMTs for broadband (300 MHz to 2 GHz) low-noise applications

A. Bouloukou\*, B. Boudjelida, A. Sobih, S. Boulay, J. Sly, M. Missous

School of Electrical and Electronic Engineering, The University of Manchester, P.O. Box 88, Manchester M60 1QD, UK

#### ARTICLE INFO

*PACS:* 85.35.Be 85.40.–e

Keywords: pHEMT InGaAs Leakage current Low noise Noise resistance

#### ABSTRACT

This paper presents the design, fabrication and characterisation of InGaAs–InAlAs high electron mobility transistors (pHEMTs) suitable for low-frequency LNA designs. Very low levels of leakage, in the order of  $0.05\,\text{A/cm}^2$ , are demonstrated by the pHEMTs, which have enabled the implementation of large-geometry, low-noise devices. Transistors with gate widths ranging from  $200\,\mu\text{m}$  to  $1.2\,\text{mm}$  are demonstrated to operate up to frequencies of  $30\,\text{GHz}$ . These are extremely promising as LNA components for implementation in broadband low-frequency systems as the very low-noise resistance simplifies matching requirements. The levels of leakage observed in our transistors further support the potential of the InGaAs/InAlAs material system as an alternative to Si when the CMOS roadmap comes to an end.

© 2008 Elsevier Ltd. All rights reserved.

#### 1. Introduction

The drive towards ever decreasing device dimensions and its consequent scaling in both vertical and lateral directions, is putting severe pressure on gate leakage currents [1]. This situation is being addressed with the use of high-k dielectric oxides in both CMOS and other advanced III–V alternatives.

The InGaAs–InAlAs pseudomorphic high electron mobility transistor (pHEMT) system occupies a prime position in the microwave and RF fields and is now seriously being considered for CMOS alternatives [2–7]. Its excellent materials properties, however, are impeded by the presence of a relatively large leakage current, which has hampered its use in applications requiring large gate periphery, such as low-frequency radio astronomy applications that have been the initial target of this work.

High-performance receiver applications have historically been implemented using only a few, cryogenically cooled, high-performance HEMTs. In such cases, minimising the

1369-8001/\$ - see front matter @ 2008 Elsevier Ltd. All rights reserved. doi:10.1016/j.mssp.2008.11.006

noise figure has been achieved through the use of small, typically  $0.1\,\mu m$ , gate-length [8–11] transistors. However, due to the very large number of receivers and wide band requirements of certain systems, one example being the Square Kilometre Array (SKA), research is now focusing on designing less expensive, room temperature-operated LNAs.

The SKA is envisaged to be a unique array-based radio telescope and its design is currently the subject of a large international effort. It is intended to provide an effective collecting area of 1 km<sup>2</sup> and to operate at frequencies from 0.15 to 25 GHz [12]. Covering this frequency range is most likely going to involve two separate antenna technologies for the lower (0.1–2 GHz) and upper (2–25 GHz) frequency bands. In this frequency range, matching the LNA for wide band, low-noise performance becomes a critical design issue as it typically requires the inclusion of large passive components that can either be integrated on-chip, acting as a source of added noise in the LNA, or implemented as off-chip components [13], increasing the overall cost. To make an MMIC LNA that is insensitive to matching across the entire band requires the use of active devices that simultaneously exhibit a low noise figure (NF) and a low noise resistance (Rn). Small gate-length InGaAs/InAlAs

<sup>\*</sup> Corresponding author. Tel.: +441613064776; fax: +441613064802. E-mail address: a.bouloukou@manchester.ac.uk (A. Bouloukou).

pHEMTs are the best candidates for achieving very low NFmin. However, the relatively high leakage currents in this material system become even more pronounced as dimensions shrink and thus prevent the use of very large periphery devices, which are needed to reduce Rn.

We report here on novel InGaAs/InAlAs pHEMTs that have been designed for use in the SKA and fabricated using conventional optical lithography. Precise material engineering of the epilayers and doping profile result in on-state leakage of  $I_{\rm g}=0.05\,{\rm A/cm^2}$ . This low leakage enables very large periphery devices (up to 1.2 mm gate width ( $W_{\rm g}$ ) and 1  $\mu$ m gate length ( $L_{\rm g}$ )) to be fabricated.

#### 2. Process technology

The pHEMT structure under investigation (wafer XMBE109) was grown, in-house, using solid-source molecular beam epitaxy (MBE) on an Oxford Instruments V90H system. It is based on an InGaAs/InAlAs/InP epitaxial layer design and consists of an InAlAs buffer, strained InGaAs channel,  $\delta$ -doped InAlAs supply and undoped InGaAs cap layer, as shown in Table 1. The Hall mobility and 2-DEG sheet carrier concentration for this sample were 12,900 cm²/V s and  $1.75\times10^{12}\,\mathrm{cm}^2$  at room temperature, respectively.

Devices were fabricated by first defining isolated mesas by means of wet-etching down to the InAlAs buffer layer, using a non-selective etch (H<sub>3</sub>PO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O). Source and drain Ohmic contacts were formed through thermal evaporation and lift-off of AuGe/Au. The gate recess was subsequently formed in a self-aligned process, using the gate-level photoresist opening as a mask. A highly selective adipic acid etch [14] was used to remove the InGaAs cap layer and form the 50 Å gate recess. The gate electrode was deposited by thermal evaporation and lift-off of Ti/Au. Ti/Au probe pads were deposited to improve the Schottky contact and enable microwave probing for on-wafer RF measurements. Airbridges were fabricated to act as source level interconnects for the multi-finger transistor and are formed through Au evaporation and lift-off.

#### 3. Results and discussion

#### 3.1. DC characteristics

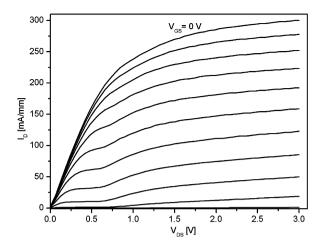

The transistors were fabricated with a gate length of  $1 \mu m$ . Typical room temperature characteristics are shown in Fig. 1. The device exhibits good output characteristics with a knee voltage of 1 V and an off-state breakdown

**Table 1** Epitaxial structure of the InGaAs/InAlAs pHEMT.

| Cap      | In <sub>0.53</sub> Ga <sub>0.47</sub> As | 5 nm   |

|----------|------------------------------------------|--------|

| Barrier  | $In_{0.52}Al_{0.48}As$                   | 30 nm  |

| δ-Doping | Si                                       | -      |

| Spacer   | In <sub>0.52</sub> Al <sub>0.48</sub> As | 10 nm  |

| Channel  | In <sub>0.7</sub> Ga <sub>0.3</sub> As   | 16 nm  |

| Buffer   | $In_{0.52}Al_{0.48}As$                   | 450 nm |

2 in S.I InP substrate.

**Fig. 1.** Typical room temperature, transistor output characteristics ( $L_{\rm g}=1~\mu m,~W_{\rm g}=200~\mu m,~V_{\rm GS}$  step =  $-0.13~\rm V$ ).

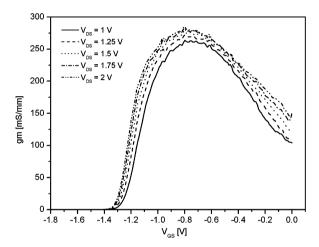

Fig. 2. Typical transconductance characteristics ( $L_{\rm g}=1\,\mu\text{m},~W_{\rm g}=200\,\text{um}).$

voltage of over 15 V. The low field source–drain resistance of this device is  $2.16\,\Omega\,\text{mm}$ , for a source–drain separation of  $5\,\mu\text{m}$  and an Ohmic contact resistance of  $0.18\,\Omega\,\text{mm}$ . The Schottky diode characteristics of the device yield an ideality factor of 1.28 and barrier height of 0.61 eV.

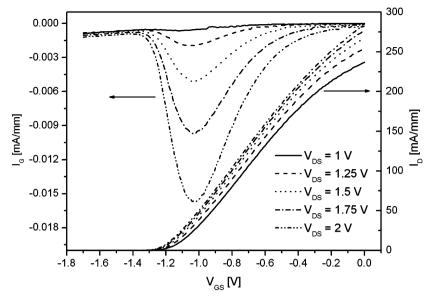

Figs. 2 and 3 show the transfer characteristics of the transistor at various bias points. The peak transconductance ( $g_{\rm m}$ ) of this device is 280 mS/mm at  $V_{\rm GS}=-0.79$  V. The on-state leakage current peaks at approximately  $V_{\rm GS}=-1$  V and ranges from 0.6 to 15.7  $\mu$ A/mm for  $V_{\rm DS}=1$  and 2 V, respectively. The characteristic bell-shaped curve of the leakage is associated with the hole current due to impact ionization. Minimal contribution of reverse leakage due to tunnelling is observed. The leakage level is 60 times lower than that reported in [15] and attests to the very low leakage currents exhibited by the new pHEMT epitaxial design. Such low levels of gate leakage indicate that it is possible to use large-geometry devices, commonly employed in high-power applications, for lownoise operation.

A. Bouloukou et al. / Materials Science in Semiconductor Processing ■ (■■■) ■■■■■■

Fig. 3. Typical on-state leakage current ( $I_G$ ) and output current ( $I_D$ ) characteristics ( $L_g = 1 \, \mu m$ ,  $W_g = 200 \, \mu m$ ).

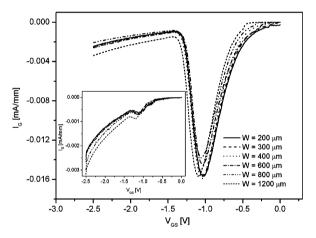

**Fig. 4.** Normalised on-state leakage current characteristics for varying device widths  $V_{\rm DS}=2\,\rm V$ . Inset shows the same characteristic for the more typical for low-noise operational bias of  $V_{\rm DS}=1\,\rm V$ .

We have fabricated devices with geometries ranging from 200  $\mu m$  to 1.2 mm in gate width, all with a nominal gate length of 1  $\mu m$ . All devices scale very well with width, as observed in the output parameters shown in Table 2, while the on-state leakage current is maintained at very low levels, shown in Fig. 4.

#### 3.2. RF characteristics

In addition to the DC characterisation of the devices, we have also analysed the microwave performance by taking measurement of small-signal S-parameters from 45 MHz to 50 GHz. Our devices exhibited typical  $f_{\rm T}$  and  $f_{\rm max}$  of 30 and 35 GHz, respectively, at a  $V_{\rm DS}=1\,{\rm V}$  and  $V_{\rm GS}=-0.84\,{\rm V}$ . The noise characteristics of this device,

based on equivalent circuit models as presented elsewhere in this issue [16], yield Rn and NF<sub>min</sub> of 5  $\Omega$  and 0.5 dB, respectively, at 2 GHz. These results further support the case for using these novel devices for low-frequency LNAs. A large-geometry (800  $\mu$ m) device is currently being used in the design and fabrication of a broadband monolithic low-noise amplifier.

## 3.3. Discussion on the suitability of the InGaAs pHEMT for CMOS applications

Looking at the device in the context of the recent investigations of III-Vs as a candidate for applications beyond the CMOS roadmap [2-7], the results also suggest that InGaAs/InAlAs pHEMTs, when designed for optimal carrier transfer to the 2DEG [17], can provide reverse leakage levels comparable to high-k/metal-gate stack structures [5,18]. At a typical bias point of  $V_{DS} = 1 \text{ V}$  and  $V_{GS} = -1$  V, the leakage current through the device is at a peak  $I_G = 0.05 \,\text{A/cm}^2$ ; within the same range as the ones shown by Datta [18] for a high-k/metal-gate stack. The leakage current density we are observing is two orders of magnitude less than reported in [19], for a 200 nm InSb QW transistor and between three and four orders of magnitude less than the values reported for 100 nm and sub-100 nm InGaAs pHEMTs in [2,3,20]. In order to achieve higher switching speeds scaling of our devices in terms of gate length is essential. With short channel effects not anticipated for up to an  $L_g$  of 200 nm (assuming an aspect ratio of 5), these levels of leakage are expected to be maintained.

#### 4. Conclusions

In conclusion, we have designed, fabricated and characterised InGaAs-InAlAs pHEMTs suitable for low-frequency

**Table 2** Comparison of the output characteristics for varying  $W_{\sigma}$  devices.

| W <sub>g</sub> (μm) | <i>V</i> <sub>T</sub> (V) | $g_{ m m}$ (mS) (at $V_{ m GS}=-0.8$ V, $V_{ m DS}=2$ V) | G <sub>m</sub> (mS/mm) | g <sub>m</sub> ratio g <sub>m</sub> /g <sub>m</sub> ,<br>200 μm | $I_{\rm dss}$ (mA/mm) (at $V_{\rm GS}=0$ V, $V_{\rm DS}=2$ V) |

|---------------------|---------------------------|----------------------------------------------------------|------------------------|-----------------------------------------------------------------|---------------------------------------------------------------|

| 1200                | -1.31                     | 342                                                      | 285                    | 6.11 ( <b>6</b> )                                               | 350                                                           |

| 800                 | -1.3                      | 222                                                      | 277                    | 3.96 ( <b>4</b> )                                               | 232                                                           |

| 600                 | -1.3                      | 178                                                      | 297                    | 3.17 ( <b>3</b> )                                               | 179                                                           |

| 400                 | -1.3                      | 118                                                      | 295                    | 2.1 ( <b>2</b> )                                                | 122                                                           |

| 300                 | -1.29                     | 84                                                       | 280                    | 1.5 ( <b>1.5</b> )                                              | 85                                                            |

| 200                 | -1.3                      | 56                                                       | 280                    | 1 (1)                                                           | 57                                                            |

The g<sub>m</sub> ratio shown in bold represents ideal values.

LNA designs. We have demonstrated that the InGaAs pHEMTs exhibit very low leakage levels with a maximum on-state leakage of 0.05 A/cm<sup>2</sup>.

The inherent low leakage of the structure enabled large-geometry, low-noise devices to be implemented, which have been hitherto difficult to realise because of the inherent low breakdown voltages of conventional InGaAs-InAlAs pHEMTs. Devices with gate widths ranging from 200 µm to 1.2 mm have been successfully demonstrated to operate up to frequencies of 30 GHz. These devices are amongst the largest ever reported in this material system for this frequency range. The significant increase in transconductance that stems from the increase in gate area translates into a large decrease in the noise resistance of these devices, making them extremely promising as LNA components for implementation in broadband low-frequency systems, such as the SKA receivers.

Further work is being done, in terms of gate length scaling, to demonstrate device operation at even higher switching speeds. However, the results presented here already show the potential of this material system as an alternative to Si when the CMOS roadmap comes to an end.

#### Acknowledgement

This work is supported by both the EC and STFC (UK) as part of the SKADS program.

#### References

- [1] Haensch W, Nowak EJ, Dennard RH, Solomon PM, Bryant A, Dokumaci OH, Kumar A, Wang X, Johnson JB, Fischetti MV. Silicon CMOS devices beyond scaling. IBM Journal of Research and Development 2006;50:339–61.

- [2] Kim D-H, Del Alamo JA, Lee J-H, Seo K-S. Performance evaluation of 50 nm in 0.7Ga0.3As HEMTs for beyond-CMOS logic applications. In: Technical Digest-International Electron Devices Meeting. Washington, DC, MD, USA: IEDM; 2005. p. 767–70.

- [3] Suemitsu T, Tokumitsu M. InP HEMT technology for high-speed logic and communications. IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences 2007;E90-C:917-22.

- [4] Kim D-H, del Alamo JA, Lee J-H, Seo K-S. Logic suitability of 50-nm In0.7Ga0.3As HEMTs for beyond-CMOS applications. IEEE Transactions on Electron Devices 2007;54:2606–13.

- [5] Chau R, Datta S, Majumdar A. Opportunities and challenges of III-V nanoelectronics for future high-speed, low-power logic applica-

- tions. In: IEEE compound semiconductor integrated circuit symposium, 2005, 4pp.

- [6] Datta S, Dewey G, Fastenau JM, Hudait MK, Loubychev D, Liu WK, Radosavljevic M, Rachmady W, Chau R. Ultrahigh-speed 0.5V supply voltage In0.7Ga0.3As quantum-well transistors on silicon substrate. IEEE Electron Device Letters 2007;28:685–7.

- [7] Bennett HS, Costa J, Immorlica Jr AA, Weitzel CE. Opportunities and challenges for indium phosphide and related materials: the international technology roadmap for semiconductors perspective. In: International conference on indium phosphide and related materials, 2005, p. 1–6.

- [8] Webber JC, Pospieszalski MW. Microwave instrumentation for radio astronomy. IEEE Transactions on Microwave Theory and Techniques 2002;50:986–95.

- [9] Smith PM, Nichols K, Kong W, MtPleasant L, Pritchard D, Lender R, Fisher J, Actis R, Dugas D, Meharry D, Swanson AW, Advances in InP HEMT technology for high frequency applications. In: International conference on indium phosphide and related materials, 13th IPRM, 2001, p. 9–14.

- [10] Pospieszalski MW, Wollack EJ. Ultra-low-noise, InP field effect transistor radio astronomy receivers: state-of-the-art. In: Proceedings of the 13th international conference on microwaves, radar and wireless communications. MIKON-2000, vol. 3; 2000. p. 23-32.

- [11] Pospieszalski MW. Extremely low-noise amplification with cryogenic FETs and HFETs: 1970–2004. IEEE Microwave Magazine 2005;6:62–75.

- [12] SKA, Square Kilometre Array—An international radio telescope for the 21st century, \( \sqrt{www.skatelescope.org/SKA\_brochure.pdf} \).

- [13] Belostotski L, Haslett JW. Noise figure optimization of inductively degenerated CMOS LNAs with integrated gate inductors. IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications 2006;53:1409–22.

- [14] Higuchi K, Uchiyama H, Shiota T, Kudo M, Mishima T. Selective wetetching of InGaAs on InAlAs using adipic acid and its application to InAlAs/InGaAs HEMTs. Semiconductor Science and Technology 1997;12:475–80.

- [15] Webster RT, Shangli W, Anwar AFM. Impact ionization in InAlAs/ InGaAs/InAlAs HEMT's. IEEE Electron Device Letters 2000;21:193–5.

- [16] Boudjelida B, Sobih A, Bouloukou A, Boulay S, Sly J, Missous M, Modeling and simulation of low-frequency broadband LNA using InGaAs/InAlAs structures: a new approach. In: E-MRS 2008 spring meeting—symposium J: beyond silicon technology: materials and devices for post-Si CMOS, Strasbourg, France, 2008.

- [17] Bouloukou A, Sobih A, Kettle D, Sly J, Missous M, Novel high-breakdown InGaAs/InAlAs pHEMTs for radio astronomy applications. In: Proceedings of the fourth ESA workshop on millimetre wave technology and applications (seventh MINT millimeter—wave international symposium), 2006, p. 221–226.

- [18] Datta S. III-V field-effect transistors for low power digital logic applications. Microelectronic Engineering 2007;84:2133-7.

- [19] Ashley T, Barnes AR, Buckle L, Datta S, Dean AB, Emery MT, Fearn M, Hayes DG, Hilton KP, Jefferies R, Martin T, Nash KJ, Phillips TJ, Tang WA, Wilding PJ, Chau R, Novel InSb-based quantum well transistors for ultra-high speed, low power logic applications, 2005, p. 2253–2256.

- [20] del Alamo JA, Kim DH, InGaAs CMOS: a "Beyond-the-Roadmap" logic technology? In: Device research conference, 2007 65th annual, 2007, p. 201–202.